|

KronoTech

PLC

Ladder Logic

Basic

Basic Motors

Counters

CTU

CTD

RET

Timer

Arithmetic

Comparison

Functions

Trig Functions

RSLogix 5000

Structured Text

HMI

Instruments

|

Introduction

In this section we will cover the count up count down and reset instruction. Counters are very essential in ladder logic programming. Counters are used to index, increment or decrement values.

Definition

The following is a list of counter instructions in SLC 500:

CTU Count UP

Symbol

Definition

- Increments the accumulated value at each false to true transition and retains the accumulated value when the instruction goes false or when power cycle occurs.

- The CTU is an instruction that counts false to true transition. When this transition happens the accumulated value is incremented by one count.

- A CTU accumulation is reset by the RES instruction.

- If the accumulation value is over the maximum range then the overflow (OV) bit will be true.

Each counter address is made of a 3-word element.

Word 1 is the control word

- Bit 0-7: Internal Use

- Bit 10: UA - Update accumulation value.

- Bit 11: UN - Underflow bit.

- Bit 12: OV - Overflow bit.

- Bit 13: DN - Done

- Bit 14: CD - Count down is enabled.

- Bit 15: CU - Count up is enabled.

Word 2 stores the preset value. (PRE)

- Specifies the value, which the counter must reach before the controller sets the done bit. When the accumulator value becomes equal to or greater than the preset value, the done status bit is set. You can use this bit to control an output device.

- Preset value is from -32,768 to 32,767

- If a timer-preset value is negative an error will occur.

Word 3 stores the accumulated value. (ACC)

- This is the number of times of false to true transitions that have occurred since the counter was last rest.

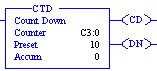

CTD Count Down

Symbol

Definition

- Decrements the accumulate value at each false to true transition and retains the accumulated value when the instruction goes false or when power cycle occurs.

- The CTD is an instruction that counts false to true transition. When this transition happen the accumulated value is decrements by one count.

- A CTD accumulation is reset by the RES instruction.

- If the accumulation value is below the minimum range then the underflow (UN) bit will be true.

· Each counter address is made of a 3-word element.

Word 1 is the control word

- Bit 0-7: Internal Use

- Bit 10: UA - Update accumulation value.

- Bit 11: UN - Underflow bit.

- Bit 12: OV - Overflow bit.

- Bit 13: DN - Done

- Bit 14: CD - Count down is enabled.

- Bit 15: CU - Count up is enabled.

Word 2 stores the preset value. (PRE)

- Specifies the value, which the counter must reach before the controller sets the done bit. When the accumulator value becomes equal to or greater than the preset value, the done status bit is set. You can use this bit to control an output device.

- Preset value is from -32,768 to 32,767

- If a timer-preset value is negative an error will occur.

· Word 3 stores the accumulated value. (ACC)

RES Reset

Symbol

Definition

- Resets the accumulated value and status bit of a timer or counter.

- Use a RES instruction to reset timers or counters. When the RES instruction is enabled, it resets the Timer On Delay, Retentive Timer, and Counter Up, Counter Down instruction having the same address as the RES instruction.

|

|