Basic Ladder Logic instructions allow very simple logical decisions. Arithmetic Ladder Logic instructions go beyond the simple true or false operation to give the ability to more complex operations. It retrieves one or more value, perform an operation and store the result in memory.

Status File

There is a very close relation between math instruction and some of the control status bits. After a math instruction is executed, the arithmetic status bits in the control status file are updated. Control status file is the data file "S2 - Status".

- S:0/0 Carry (C) Sets if carry is generated; otherwise it is cleared.

- S:0/1 Overflow (V) Indicates that the actual result of a math instruction does not fit in the designated destination

- S:0/2 Zero (Z) Indicates a 0 value after a math, move or a logic instruction

- S:0/3 Sign (S) Indicates a negative value after a math, move or logic instruction.

- S:5/0 Minor Error Minor error bit is set upon detection of a mathematical overflow, or division by zero. This error can cause a CPU fault, which could be avoided if the bit is unlatched before the END, TND, or REF statement.

- S:13S:14 Math register S:13 -Contains the least significant word of the 32 bit values of MUL, DDV, FRD, and TODS:14 -Contains the Most significant word of the 32 bit values of MUL, DDV, FRD and TOD

Definition

The following is a list of the comparison instructions in SLC 500:

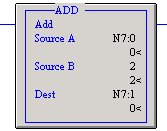

Symbol

Definition

When rung conditions are true, this output instruction adds Source A to Source B and stores the result at the destination address. Source A and Source B can either be values or addresses that contain values, however Source A and Source B cannot both be constants.

- Carry (C), Sets if carry is generated; otherwise resets. Cleared For floating value

- Overflow (V), Sets if underflow; otherwise resets

- Zero (Z), Sets if the result is Zero; otherwise resets;

- Sign (S), Sets if result is negative; otherwise resets;

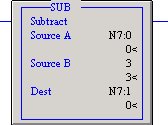

Symbol

Definition

When rung conditions are true, the SUB output instruction subtracts Source B from Source A and stores the result in the destination. Source A and Source B can either be values or addresses that contain values, however Source A and Source B cannot both be constants.

- Carry (C), Sets if borrow is generated; otherwise resets. Cleared For floating value

- Overflow (V), Sets if underflow; otherwise resets

- Zero (Z), Sets if the result is Zero; otherwise resets;

- Sign (S), Sets if result is negative; otherwise resets;

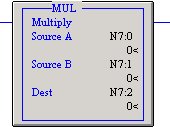

Symbol

Definition

Use the MUL instruction to multiply one value (source A) by another (source B) and place the result in the destination. Source A and Source B can either be constant values or addresses that contain values, however Source A and Source B cannot both be constants.

The math register contains the 32-bit signed integer result of the multiply operation. This result is valid at overflow.

- Carry (C), Always reset

- Overflow (V), Sets if overflow; otherwise resets

- Zero (Z), Sets if the result is Zero; otherwise resets;

- Sign (S), Sets if result is negative; otherwise resets;

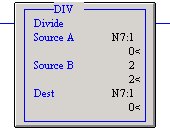

Symbol

Definition

When rung condition is true, this output instruction divides Source A by Source B and stores the result in the destination and the math register. The value stored in the destination is rounded. The value stored in the math register consists of the unrounded quotient (placed in the most significant word) and the remainder (placed in the least significant word).

Source A and Source B can either be constant values or addresses that contain values, however Source and Source B cannot both be constants.

- Carry (C), Sets if carry is generated; otherwise resets. Cleared For floating value

- Overflow (V), Sets if division by zero or overflow; otherwise resets

- Zero (Z), Sets if the result is Zero; otherwise resets, undefined if overflow

- Sign (S), Sets if result is negative; otherwise resets; undefined if overflow.

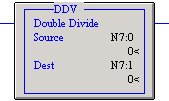

Symbol

Definition

When rung conditions are true, this output instruction divides the contents of the math register (S:13 and S:14), containing 32 bits of data, by the source (16 bits of data) and stores the result in the destination and the math register.

The math register initially contains the dividend of the DDV operation. Upon execution the unrounded quotient is placed in the most significant word of the math register. The remainder is placed in the least significant word of the math register.

- Carry (C), Sets if carry is generated; otherwise resets. Cleared For floating value

- Overflow (V), Sets if division by zero or result > 32 767 or < 32768; otherwise resets

- Zero (Z), Sets if the result is Zero; otherwise resets;

- Sign (S), Sets if result is negative; otherwise resets; undefined if overflow.